MC145151-2 and MC145152-2

PLL Frequency Synthesizers

(CMOS)

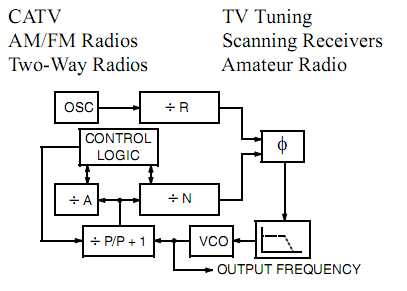

Устройства, описанные в этом документе, обычно используется как маломощный синтезатор, с фазовой автоподстройкой частоты. В сочетании с внешним ФНЧ фильтром и генератором, управляемым напряжением, эти устройства могут обеспечить все функции до предельной частоты работы устройства. Для работы с более высокой частотой VCO используйте понижающий микшер или делитель между VCO и микросхемой синтезатора.

Эти микросхемы частоты могут найти применение в следующих приложениях:

1 MC145151-2 с параллельным входом (интерфейсы с одномодульными предделителями)

1.1 Возможности

1.2 Описание контактов

1.3 Типичные приложения

2 MC145152-2 с параллельным входом (интерфейсы с двухмодульными предделителями)

2.1 Особенности

2.2 Описание контактов

2.3 Типичные приложения

3 Электрические характеристики MC145151-2 и MC145152-2

4 Рекомендации по проектированию

4.1 Контур фазовой автоподстройки частоты - конструкция фильтра нижних частот

4.2 Рекомендации по использованию кварцевого осциллятора

4.3 Предварительное масштабирование двойного модуля упругости

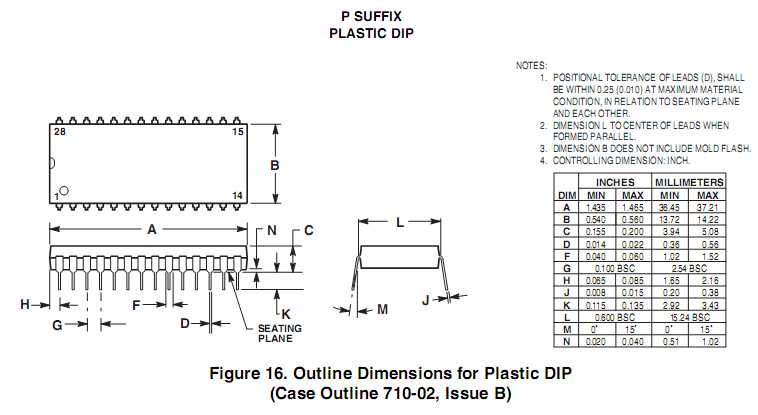

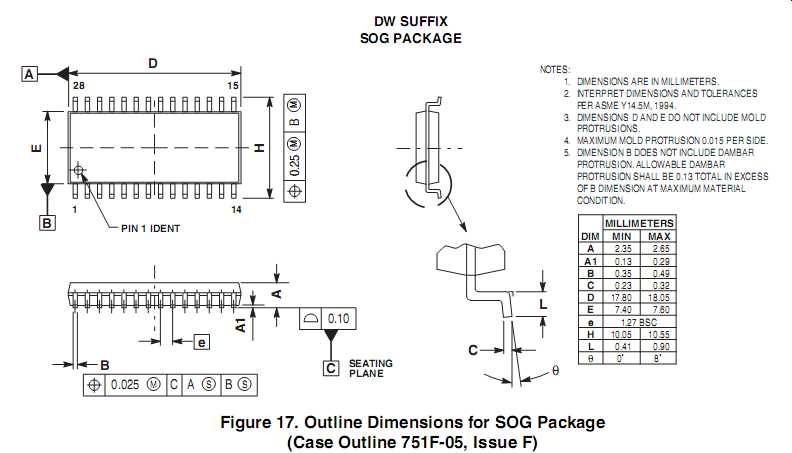

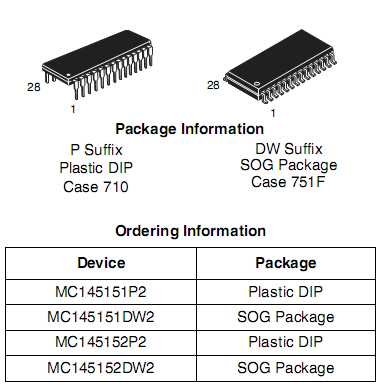

5 Размеры упаковки

1. MC145151-2 с параллельным входом (интерфейсы с одномодульными предделителями)

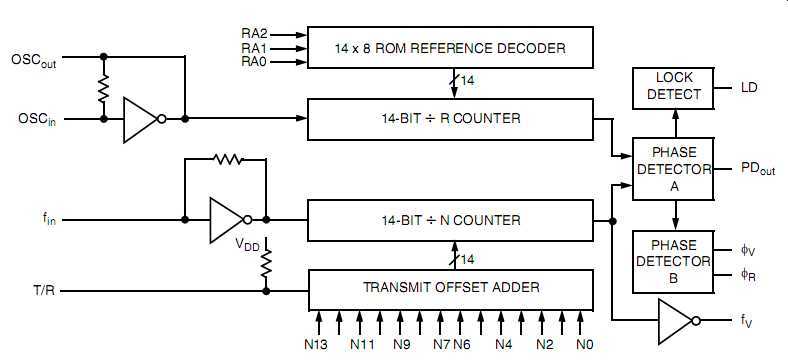

MC145151-2 программируется 14 линиями параллельного ввода данных для счетчика N и тремя линиями ввода для счетчик R. Устройство имеет состоять из опорного генератора, выбираемые-делитель опорной частоты, цифровой фазовый детектор и 14-битный программируемый счетчик деления на N.

MC145151-2 - это улучшенная замена MC145151-1. Мощность потребление снизилось, а характеристики ESD и фиксации улучшились.

1.1 Особенности- Диапазон рабочих температур: от -40 до 85 ° C

- Низкое энергопотребление за счет использования технологии CMOS

- Диапазон питания от 3,0 до 9,0 В

- По графику или с Chip Ссылка Осциллятор работы

- Блокировка сигнала обнаружения

- Доступен выход ÷N счетчика

- Одномодульное/параллельное программирование

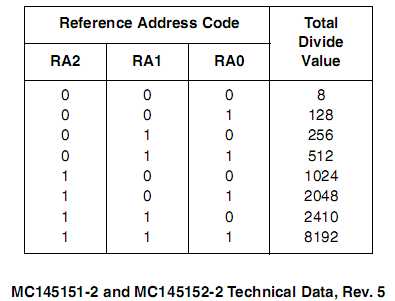

- 8 Выбирается пользователем/ Значения ÷R: 8, 128, 256, 512, 1024, 2048, 2410, 8192

- Диапазон ÷N = от 3 до 16383

- «Линеаризованный» цифровой фазовый детектор улучшает линейность передаточной функции

- Два варианта сигнала ошибки: односторонний (с тремя состояниями) или двусторонний

- Сложность микросхемы: 8000 полевых транзисторов или 2000 эквивалентных вентилей

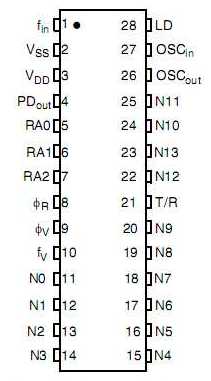

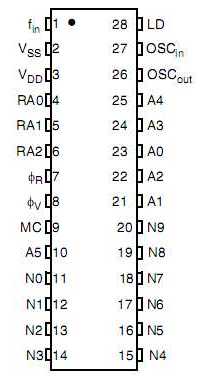

Рисунок 1. Обозначение выводов

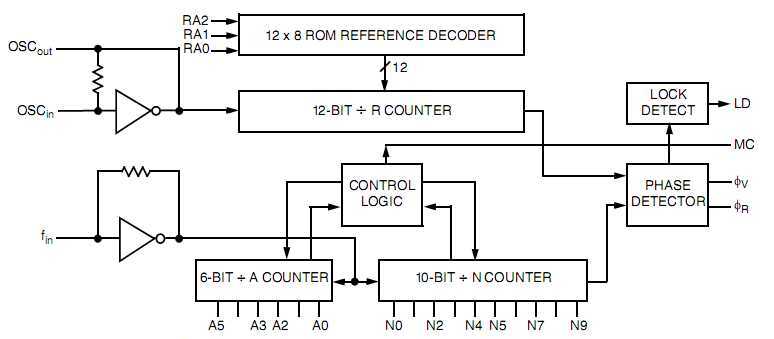

Рисунок 2. Блок диаграмма MC145151-2

ПРИМЕЧАНИЕ. Входы N0 - N13 и входы RA0, RA1 и RA2 имеют подтягивающие резисторы, которые не показаны.

1.2.1 Входные выводы

fin

Вход частоты (Pin 1)

Вход в ÷N часть синтезатора. плавник обычно выводится из контура ГУН и подключается по переменному току к устройству. Для сигналов с большей амплитудой (стандартные логические уровни КМОП) может использоваться связь по постоянному току.

RA0 - RA2Ссылочный адресные входы (выводы 5, 6, 7)

Эти три входа устанавливают код, определяющий одно из восьми возможных значений деления для общего задания. разделитель, как определено в таблице ниже.

Подтягивающие резисторы гарантируют, что входы, оставленные открытыми, остаются на уровне логической 1 и требуют только переключателя SPST для перевода данных в нулевое состояние.

N входов программирования счетчиков (контакты 11-20, 22-25)

Эти входы предоставляют данные, которые предварительно установлены в? N счетчик, когда он достигает счетчика нуля. N0 - это наименее значимый, а N13 - наиболее значимый. Подтягивающие резисторы гарантируют, что входы, оставленные открытыми, остаются при логической 1 и требует только переключателя SPST для перевода данных в нулевое состояние.

Т/РВход сумматора смещения передачи/приема (контакт 21)

Этот вход управляет смещением, добавляемым к данным, предоставленным на N входах. Обычно это используется для компенсации частоту ГУН на величину, равную частоте ПЧ трансивера. Это смещение зафиксировано на 856 когда T/R низкий, и не дает смещения, когда T/R высокий. Подтягивающий резистор гарантирует, что соединение не будет отображаются как логическая 1, не вызывая сложения смещения.

OSCin, OSCoutГенератор опорной частоты вход/выход (выводы 27, 26)

Эти контакты образуют встроенный опорный генератор при подключении к клеммам внешнего параллельного резонансный кристалл. Конденсаторы установки частоты соответствующего номинала должны быть подключены от OSCin к земля и OSCout на землю. OSCin также может служить входом для внешнего сигнала. Этот сигнал обычно связан по переменному току с OSCin, но для сигналов с большей амплитудой (стандартная логика CMOS уровней) также может использоваться связь по постоянному току. В режиме внешнего задания подключение к OSCout не требуется.

1.2.2 Выходные выводы

PDout

Выход фазового детектора А (контакт 4)

Трехпозиционный выход фазового детектора для использования в качестве сигнала ошибки контура. Также доступны двусторонние выходы для этой цели (см.φV и φR).

Частота fV > fR или fV опережение: отрицательные импульсы

Частота fV < fR или fV запаздывание: положительные импульсы

Частота fV = fR и совпадение фаз: состояние с высоким импедансом

φR, φV

Выход фазового детектора B (контакт 8, 9)

Эти выходы фазового детектора могут быть объединены извне для сигнала ошибки контура. Несимметричный выход также доступен для этой цели (см. PDout).

Если частота fV больше fR или если фаза fV является опережающей, то информация об ошибке предоставляется с помощью φV пульсирующий низкий. φR остается существенно высоким.

Если частота fV меньше fR или если фаза fV отстает, то информация об ошибке предоставляется с помощью φR пульсирующий низкий. φV остается существенно высоким.

Если частота fV = fR и оба находятся в фазе, то оба φV и φR остаются высокими, за исключением небольшого минимальный период времени, когда оба импульса находятся в низкой фазе.

fV Выход счетчика N (контакт 10)Это буферизованный вывод команды cчетчик ÷N, который внутренне подключен к входу фазового детектора. С участием этот выход доступен, Счетчик ÷N можно использовать независимо.

LDВыход детектора блокировки (контакт 28)

По существу высокий уровень, когда петля заблокирована (fR, fV той же фазы и частоты). Низкие импульсы при петле вне блокировки.

1.2.3 Источник питания

VDD

Положительный источник питания (контакт 3)

Положительный потенциал источника питания. Этот вывод может находиться в диапазоне от +3 до +9 В относительно VSS.

VSS

Отрицательный источник питания (контакт 2)

Самый отрицательный потенциал предложения. Этот штифт обычно заземлен.

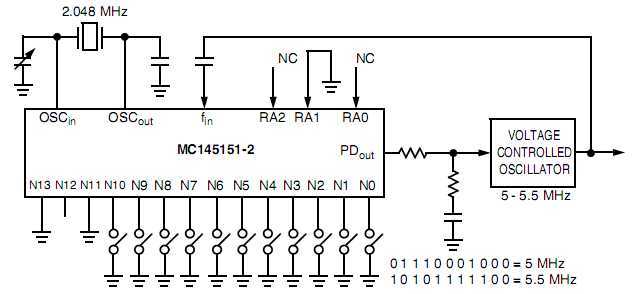

1.3 Типичные приложения

Рисунок 3. Генератор диапазона 5 - %,5 МГц с шагом перестройки 1 КГц

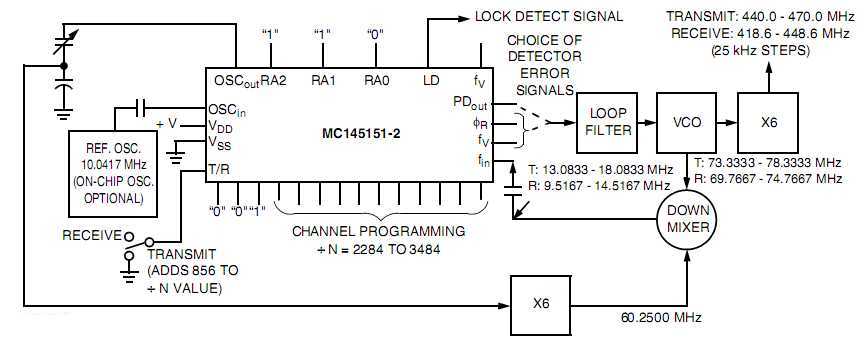

Рисунок 4. Синтезатор для диапазонов UHF наземной мобильной радиосвязи

1. fR = 4,1667 кГц; ÷R = 2410; Подвод низких частот 21,4 МГц во время приема.

2. Показанные значения частот относятся к диапазону 440–470 МГц.

Аналогичная реализация применима к полосе 406–440 МГц.

Для 470-512 МГц, рассмотрим опорную частоту генератора X9 для инжекционного смесителя сигнала (90,3750 МГц).

2. MC145152-2 с параллельным входом (интерфейсы с двухмодульными предделителями)

MC145152-2 запрограммирован шестнадцатью параллельными входами для счетчиков N и A и тремя входными линиями для счетчика R. Устройство имеет состоять из опорного генератора, выбираемый-делитель опорной частоты, два-выход фазового детектора, 10-битного программируемого деления на N счетчика, и 6-бит программируемый деления на счетчик.

MC145152-2 - это улучшенная замена MC145152-1. Снизилось энергопотребление, улучшились характеристики электростатического разряда и фиксации.

2.1 Особенности

- Диапазон рабочих температур: от -40 до 85 ° C

- Низкое энергопотребление за счет использования технологии CMOS

- Диапазон питания от 3,0 до 9,0 В

- On/Off-Chip работа эталонного осциллятора

- Сигнал обнаружения блокировки

- Двойной модуль/параллельное программирование

- 8 выбираемых пользователем значений ÷R: 8, 64, 128, 256, 512, 1024, 1160, 2048

- ÷N диапазон = от 3 до 1023,÷A диапазон = от 0 до 63

- Сложность микросхемы: 8000 полевых транзисторов или 2000 эквивалентных вентилей

Рисунок 6. Блок-схема MC145152-2.

2.2 Описание выводов

2.2.1 Входные выводы

fin

Вход частоты (вывод 1)

Вход по положительному фронту срабатывает счетчики ÷N и ÷A. плавник обычно получается из двойного модуля прескалер и подключен к устройству по переменному току. Для сигналов с большей амплитудой (стандартные логические уровни CMOS). Может использоваться связь по постоянному току.

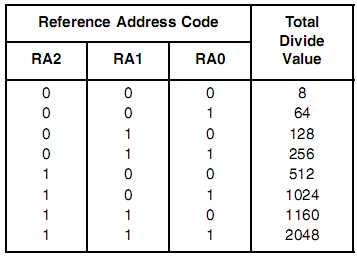

RA0, RA1, RA2Ссылочный адресные входы (выводы 4, 5, 6)

Эти три входа устанавливают код, определяющий одно из восьми возможных значений деления для общего задания. разделитель. Общие контрольные значения деления следующие:

N входы для программирования счетчиков (контакты 11-20)

Входы N предоставляют данные, которые предварительно устанавливаются в счетчик ÷N, когда он достигает счетчика 0. N0 - это наименьшая значащая цифра, а N9 - наиболее значимая. Подтягивающие резисторы гарантируют, что входы, оставленные открытыми, остаются при логической 1 и требует только переключателя SPST для перевода данных в нулевое состояние.

A0-A5A входы программирования счетчика (контакты 23, 21, 22, 24, 25, 10)

Входы A определяют количество тактов fin, для которых требуется логический 0 на выходе MC (см. Раздел 4.3, «Предварительное масштабирование двойного модуля упругости» на стр. 21). Все входы A имеют внутренние подтягивающие резисторы, которые убедитесь, что входы, оставленные открытыми, останутся на логической 1.

OSCin, OSCoutГенератор опорной частоты вход/выход (выводы 27, 26)

Эти контакты образуют встроенный опорный генератор при подключении к клеммам внешнего параллельного резонансный кристалл. Конденсаторы установки частоты соответствующего номинала должны быть подключены от OSCin к земля и OSCout на землю. OSCin также может служить входом для внешнего сигнала. Этот сигнал обычно связан по переменному току с OSCin, но для сигналов с большей амплитудой (стандартная логика CMOS уровней) также может использоваться связь по постоянному току. В режиме внешнего задания подключение к OSCout не требуется.

2.2.2 Выходные выводыφR, φV Выходы фазового детектора B (контакты 7, 8)

Эти выходы фазового детектора могут быть объединены извне для сигнала ошибки контура.

Если частота fV больше fR или если фаза fV является опережающей, то информация об ошибке предоставляется φV пульсирует с низким уровнем. φR остается существенно высоким.

Если частота fV меньше fR или если фаза fV отстает, то информация об ошибке предоставляется с помощью φR пульсирующий низкий. φV остается существенно высоким.

Если частота fV = fR и оба находятся в фазе, то оба φV и φR остаются высокими, за исключением небольшого минимальный период времени, когда оба импульса находятся в низкой фазе.

MC

Выход управления предварительным масштабированием с двумя модулями упругости (вывод 9)

Сигнал, генерируемый встроенной логической схемой управления для управления внешним двухмодульным предварительным делителем.

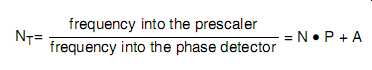

Уровень MC будет низким в начале цикла счета и останется низким до ÷A Счетчика имеет

отсчитывается от его запрограммированного значения. В это время MC становится высоким и остается высоким до ÷N

счетчик отсчитал оставшуюся часть пути от своего запрограммированного значения (N - дополнительные отсчеты, поскольку

обе ÷N и ÷A ведут обратный отсчет в течение первой части цикла). MC затем понижается,

счетчики предварительно устанавливаются на соответствующие запрограммированные значения, и повторяется вышеуказанная последовательность. Это предусматривает общее программируемое значение деления (NT) = N • P + A, где P и P + 1 представляют двухмодульный предварительный делитель разделите значения соответственно для высокого и низкого уровней MC, N - число, запрограммированное в Счетчик ÷N, а номер запрограммирован в Счетчик ÷A.

Выход детектора блокировки (контакт 28)

По существу высокий уровень, когда петля заблокирована (fR, fV той же фазы и частоты). Низкие импульсы при петле вне блокировки.

2.2.3 Источник питания

VDD

Положительный источник питания (контакт 3)

Положительный потенциал источника питания. Этот вывод может находиться в диапазоне от +3 до +9 В относительно VSS.

VSS

Отрицательный источник питания (контакт 2)

Самый отрицательный потенциал питания. Этот вывод обычно заземлен.

2.3 Типичные приложения

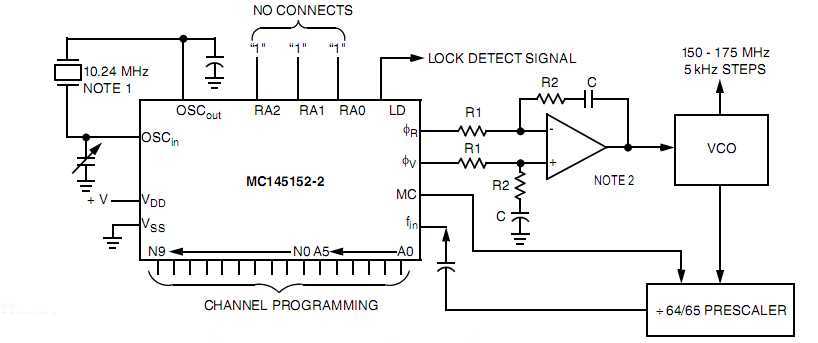

Рисунок 7. Синтезатор для наземной мобильной радиосвязи в УКВ диапазонах

1. Дополнительный генератор вне кристалла.

2. Выходы φR и φV подаются на внешний сумматор/контурный фильтр. См. Страницу "Контур фазовой автоподстройки частоты - ФНЧ" для дополнительной информации. Выходы φR и φV переключаются по схеме "rail-to-rail".

Следовательно, пользователь должен быть осторожен, чтобы не выйти за пределы входного диапазона синфазного сигнала операционного усилителя, используемого в сумматоре/контурном фильтре.

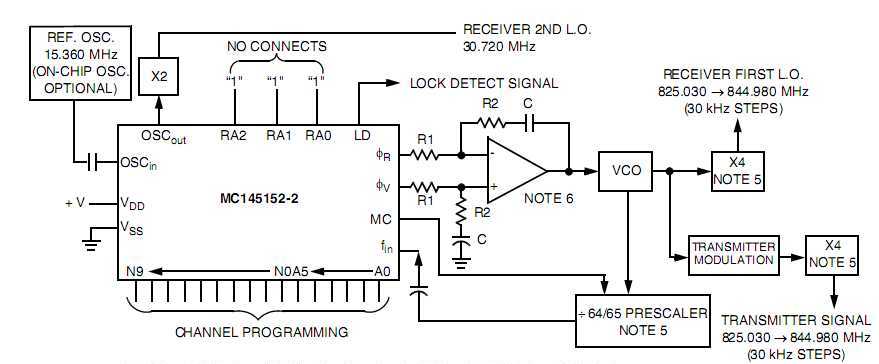

Рис. 8. 666-канальный управляемый компьютером синтезатор мобильного радиотелефона для сотовых радиосистем 800 МГц

1.Приемник 1-й I.F. = 45 МГц, инжекция на стороне низких частот; Ресивер 2-й I.F. = 11,7 МГц, инжектор на стороне нижней боковой.

2. Дуплексный режим с разделением прием/передача 45 МГц.

3.fR = 7,5 кГц; R = 2048.

4.Ntotal = N • 64 + A = от 27501 до 28166; N = 429-440; A = от 0 до 63.

5. Высокочастотные предделители могут использоваться для более высокочастотных реализаций VCO и fref.

6. Выходы φR и φV подаются на внешний сумматор/контурный фильтр. Дополнительную информацию см. На странице «Контур фазовой автоподстройки частоты - конструкция фильтра нижних частот». Выходы φR и φV переключаются по схеме "rail-to-rail". Следовательно, пользователь должен быть осторожен, чтобы не выйти за пределы входного диапазона синфазного сигнала операционного усилителя, используемого в сумматоре/контурном фильтре.

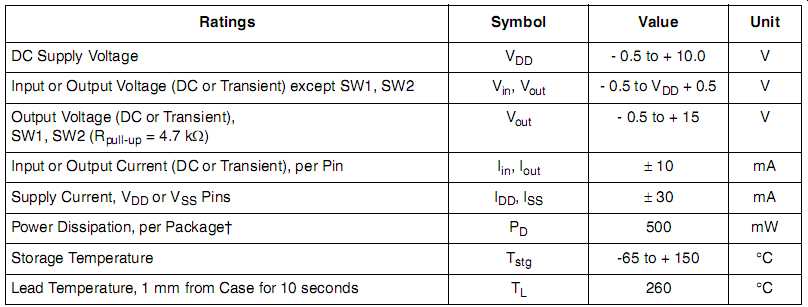

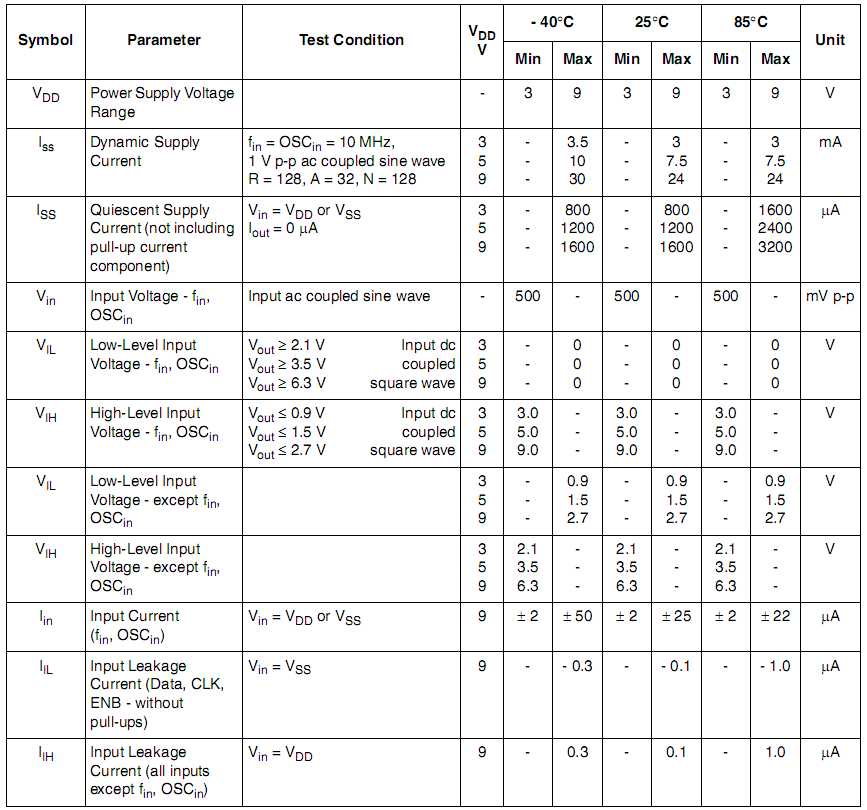

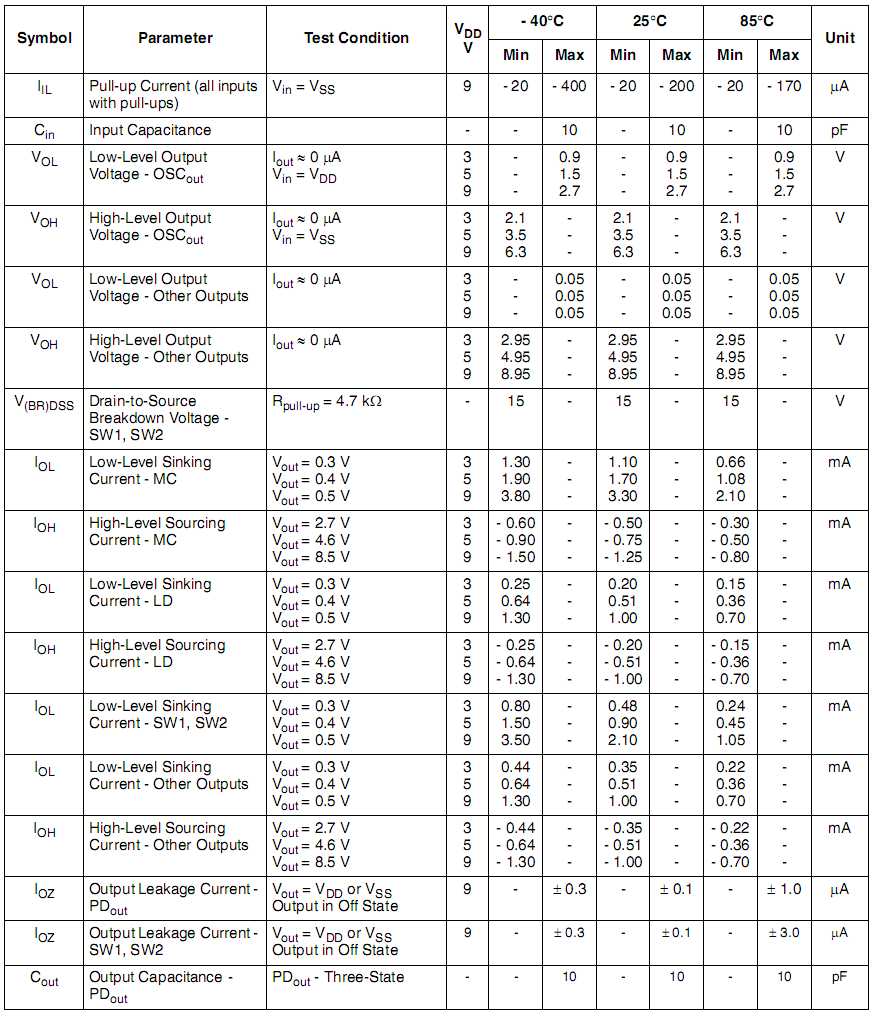

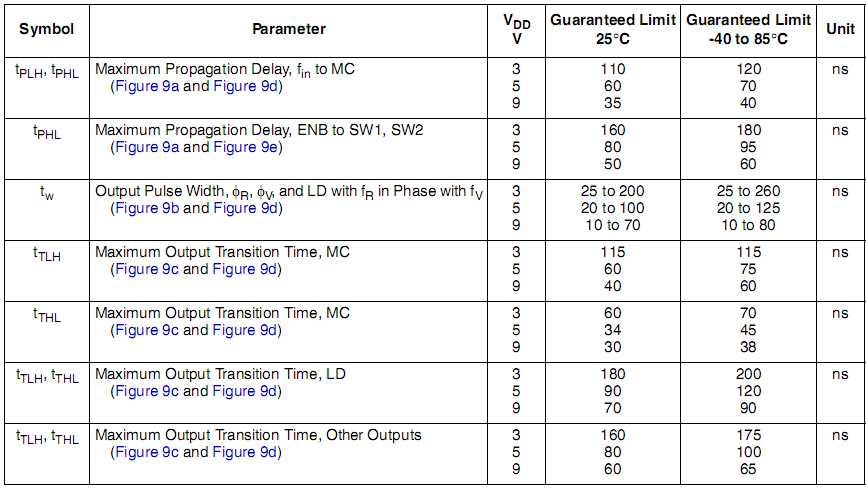

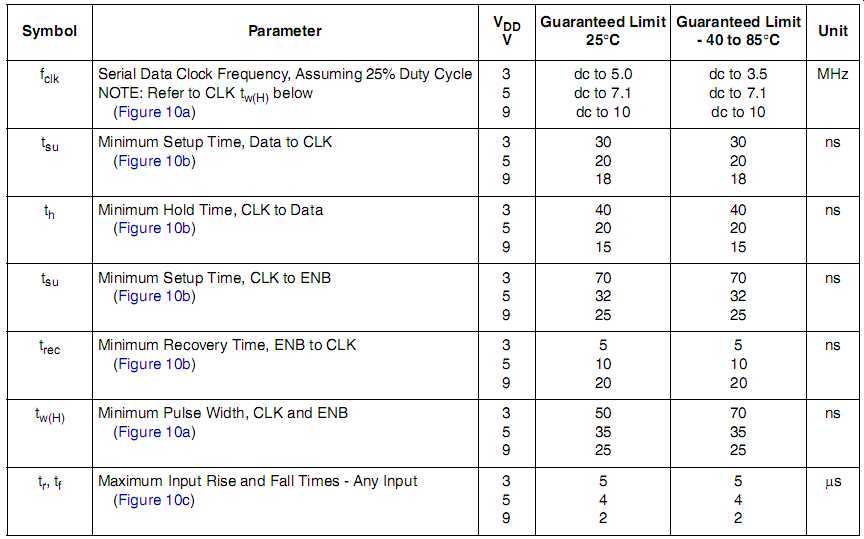

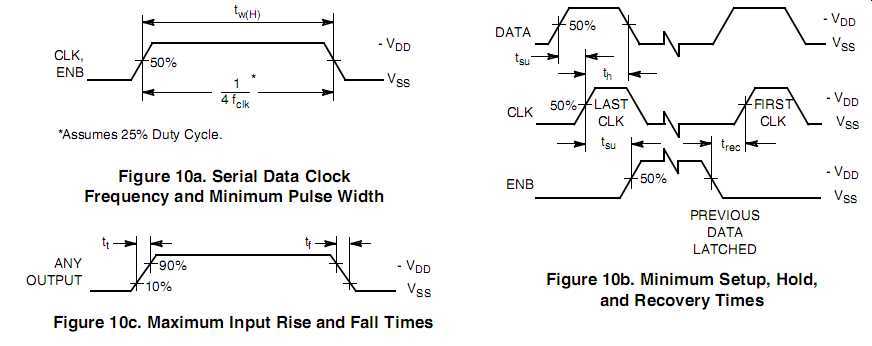

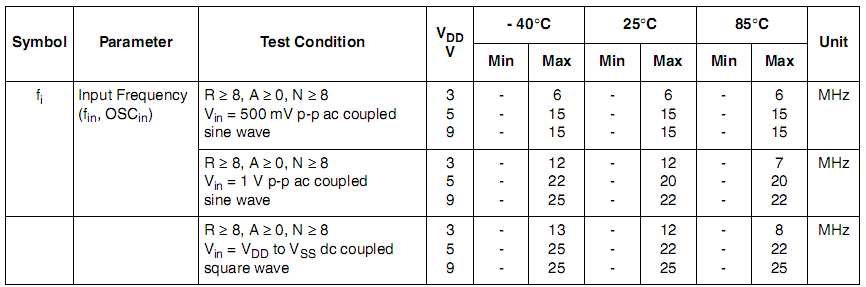

3. Электрические характеристики MC145151-2 и MC145152-2

Эти устройства содержат схему защиты для защиты от повреждений из-за высокого статического напряжения или электрического поля. Однако следует принимать меры предосторожности, чтобы избежать приложений с напряжением выше максимального. Номинальные напряжения для этих цепей с высоким импедансом. Для правильной работы Vin и Vout должен быть ограничен диапазоном VSS ≤ (Vin or Vout) ≤ VDD, кроме SW1 и SW2.

SW1 и SW2 могут быть связаны через внешние резисторы с напряжением до 15 В, независимо от источника питания. напряжение.

Неиспользуемые входы всегда должны быть привязаны к соответствующему уровню логического напряжения (например, VSS или VDD), за исключением для входов с подтягивающими устройствами. Неиспользуемые выходы должны быть оставлены открытыми.

Таблица 1. Максимальные режимы работы

(Напряжения, указанные в VSS)

† Снижение температуры рассеиваемой мощности:

Пластиковый DIP: - 12 мВт/°C от 65 до 85°C

Пакет SOG: - 7 мВт/°C от 65 до 85°C

Таблица 2. Электрические характеристики

(Напряжения, указанные в VSS)

Примечание: Обычно задержка распространения ФАПЧ от плавника до MC плюс время настройки предварительного делителя определяет верхнюю частоту предела системы. Верхний предел частоты находится по следующей формуле: f=P/(tP+tset), где f - верхняя частота в Гц, P - нижний из двух коэффициентов предварительного делителя модуля упругости, tP - задержка распространения от плавника до MC в секундах, а tset - время настройки предварительного делителя в секундах. Например, при питании 5 В задержка от плавника до MC составляет 70 нс. Если используется предварительный делитель MC12028A, время настройки составляет 16 нс. Таким образом, если используется соотношение 64/65, верхний предел частоты равен f=P/(tP+tset)=64/(70+16)=744 МГц.

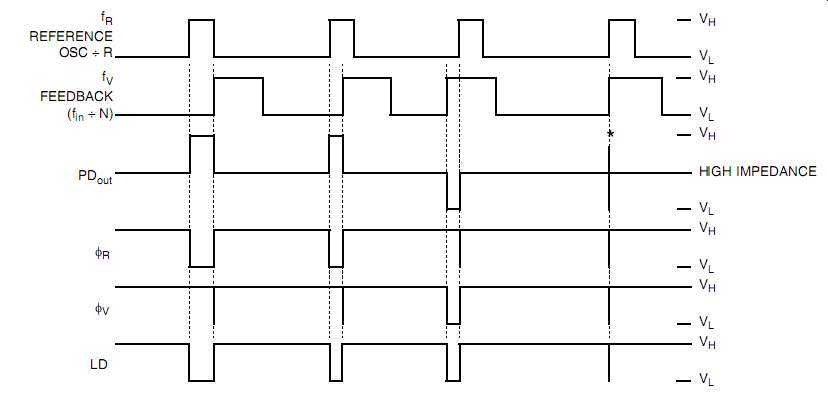

Рисунок 11. Формы выходных сигналов фазового детектора/блокировки детектора

VL = уровень низкого напряжения.

* В этот момент, когда и fR, и fV находятся в фазе, выходной сигнал приближается к среднему значению.

ПРИМЕЧАНИЕ: PDout генерирует импульсы ошибки во время блокировки. Когда синхронизирован по фазе и частоте, выходной сигнал высокий, а напряжение на этом выводе определяется конденсатором фильтра нижних частот.

4. Рекомендации по проектированию

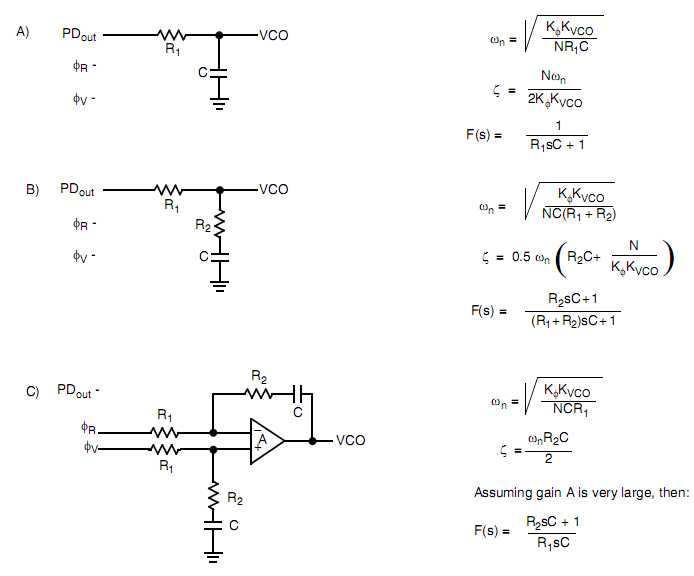

4.1 Контур фазовой автоподстройки частоты - конструкция фильтра нижних частот

Рисунок 12. Контур фазовой автоподстройки частоты - конструкция фильтра нижних частот.

Выходы φR и φV переключаются по схеме "rail-to-rail". Таким образом, пользователь должен быть осторожен, чтобы не выйти за пределы входного диапазона синфазного сигнала ОУ, используемый в сумматоре/контурном фильтре.

Определения:

N = общий коэффициент деления в контуре обратной связи

Кφ (Коэффициент усиления фазового детектора) = VDD/4π для PDout

Кφ (Коэффициент усиления фазового детектора) = VDD/2π для φV и φR KVCO (усиление VCO) = 2π∧ fVCO/∧VVCO

для типичного дизайна wn (собственная частота) = 2πfr/10 (на входе фазового детектора).

Коэффициент демпфирования:ς ≡ 1

4.2 Соображения по поводу кристаллического осциллятора

Следующие опции могут быть рассмотрены, чтобы обеспечить заданную частоту с частотой CMOS компании Freescale синтезаторы.

4.2.1 Использование гибридного кварцевого генератора

Имеющиеся в продаже кварцевые генераторы с температурной компенсацией (TCXO) или кварцевые генераторы данных тактовые генераторы обеспечивают очень стабильные опорные частоты. Осциллятор, способный опускаться и добывать 50 мкА на логических уровнях КМОП могут быть подключены к OSCin напрямую или по постоянному току. В целом самая высокая частота возможность достигается за счет использования прямоугольного сигнала с прямой связью, имеющего напряжение между рельсами (от VDD до VSS) качели. Если генератор не имеет логических уровней CMOS на выходах, емкостная связь или связь по переменному току с OSCin может быть использовано. OSCout, небуферизованный выход, следует оставить плавающим.

4.2.2 Создание справочника вне кристаллаПользователь может разработать внешний кварцевый генератор, используя микросхемы, специально разработанные для приложений кварцевого генератора, или дискретные транзисторы. Опорный сигнал генератора передается по переменному току на OSCin.

Для сигналов большой амплитуды (стандартные логические уровни КМОП) используется связь по постоянному току. OSCout, небуферизованный выход, следует оставить плавающим. Как правило, наивысшие частотные характеристики достигаются с прямоугольной волной с прямой связью, имеющей размах напряжения между фазами питания.

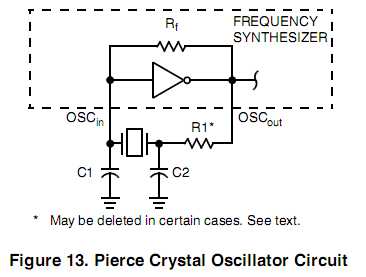

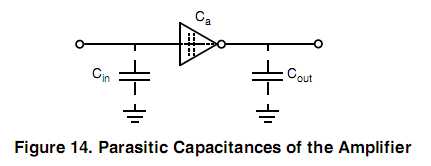

4.2.3 Использование схемы встроенного генератораУсилитель на кристалле (цифровой преобразователь) вместе с соответствующим кристаллом может быть использован, чтобы обеспечить частоту опорного источника. Кристалл основной моды, параллельный резонанс при желаемой рабочей частоты, следует подключать, как показано на рисунке 13.

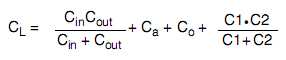

Для VDD = 5,0 В кристалл должен быть указан для нагрузочной емкости CL, которая не превышает 32 пФ для частот приблизительно до 8,0 МГц, 20 пФ для частот в диапазоне от 8,0 до 15 МГц и 10 пФ для более высоких частот. Это рекомендации, которые обеспечивают разумный компромисс между емкостью ИС, возможностями привода, отклонениями паразитной емкости и входной/выходной емкости ИС и реалистичными значениями CL. Емкость шунтирующей нагрузки CL, представленная на кристалле, может быть оценена как:

Cin = 5 пФ (см. Рисунок 14)C1 и C2 = внешние конденсаторы (см. Рисунок 13)

Cout = 6 пФ (см. Рисунок 14)

Ca = 1 пФ (см. Рисунок 14)

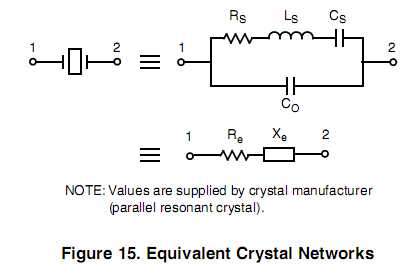

CO = емкость держателя кристалла (см. Рисунок 15)

Частоту генератора можно «подрезать», сделав часть или всю переменную C1. Кристалл и связанные с ним компоненты должны быть расположены как можно ближе к выводам OSCin и OSCout, чтобы минимизировать искажения, паразитную емкость, паразитную индуктивность и время стабилизации запуска. В некоторых случаях паразитная емкость должна быть добавлена к значению Cin и Cout.

Мощность рассеивается в эффективном последовательном сопротивлении кристалла Re на рисунке 15. Уровень возбуждения, указанный производителем кристалла, представляет собой максимальное напряжение, которое кристалл может выдержать без повреждений или чрезмерный сдвиг частоты. R1 на Рисунке 13 ограничивает уровень возбуждения. В некоторых случаях использование R1 может не потребоваться (например, R1 = 0 Ом).

Чтобы убедиться, что максимальное напряжение питания постоянного тока не приводит к перегрузке кристалла, контролируйте выходную частоту как функцию напряжения на OSCout. (Следует соблюдать осторожность, чтобы минимизировать нагрузку.) Частота должна очень незначительно увеличиваться при увеличении напряжения питания постоянного тока. Перегруженный кристалл будет уменьшать частоту или становиться нестабильным с увеличением напряжения питания. Рабочее напряжение питания должно быть уменьшено или значение R1 должно быть увеличено, если существует перегрузка. Пользователь должен учитывать, что время запуска генератора пропорционально значению R1.

В процессе поставки кристаллов для использования с КМОП-инверторами многие производители кристаллов накопили опыт в разработке КМОП-генераторов с кристаллами. Обсуждения с такими производителями могут оказаться очень полезными.

4.3 Предварительное масштабирование двойного модуля4.3.1 Обзор

Метод двухмодульного предварительного масштабирования хорошо зарекомендовал себя как метод достижения высокопроизводительной работы синтезатора частот на высоких частотах. По сути, подход позволяет использовать относительно низкочастотные программируемые счетчики в качестве высокочастотных программируемых счетчиков с быстродействием в несколько сотен МГц. Это возможно без ущерба для разрешения системы и производительности, которые возникают, если для предварительного делителя используется фиксированный (одномодульный) делитель.

При двухмодульном предварительном масштабировании счетчики более низкой скорости должны быть настроены однозначно. Необходима специальная логика управления, чтобы выбрать значение деления P или P + 1 в предварительном делителе на необходимое количество времени (см. Определение управления модулем).

4.3.2 Рекомендации по проектированию

Общее значение деления системы, Ntotal (NT), будет определяться приложением:

N номер запрограммирован в ÷N счетчик, A номер запрограммирован в ÷A Счетчик, P и P + 1 - это два выбираемых коэффициента деления, доступных в двухмодульных предварительных делителях. Чтобы иметь последовательность значений NT, знак ÷A cчетчика программируется от нуля до P - 1 для определенного значения N Счетчика ÷N. Затем N увеличивается до N + 1, а знак ÷A снова упорядочивается от 0 до P - 1.

Существуют минимальные и максимальные значения, которые могут быть достигнуты для NT. Эти значения зависят от P и размера ÷N и ÷A Счетчика.Ограничение N? Всегда применяется. Если Amax=P-1, то Nmin≥P-1. Тогда NTmin=(P-1) P + A или (P - 1) P, поскольку A может принять значение 0.

NTmax = Nmax • P + Amax

Чтобы максимизировать частотную способность системы, выходной сигнал двухмодульного предварительного делителя должен изменяться от низкого до высокого после каждой группы входных циклов P или P + 1. Предделитель должен делиться на P, когда его линия управления модулем высокий и P + 1, когда его MC низкий.

Для максимальной частоты предделителя (fVCOmax) значение, используемое для P, должно быть достаточно большим, чтобы:1. fVCOmax, деленное на P, не может превышать частотную характеристику fin (ввод для счетчиков ÷N и ÷A).

2. Период fVCO, деленный на P, должен быть больше суммы времен:

а) Задержка распространения через двухмодульный предварительный делитель.

б) Время установки или восстановления предделителя относительно его сигнала MC.

c) Время распространения сигнала от плавника до выхода MC для устройства синтезатора частоты.

Иногда полезного упрощения программного кода можно достичь, выбрав для P значения 8, 16, 32 или 64. В этих случаях желаемое значение NT получается, когда NT в двоичном формате используется в качестве программного кода для ÷N и ÷А счетчики обрабатываются следующим образом:

1. Допустим, что ÷A Счетчик содержит биты «а», где 2а≥ P.

2. Всегда программировать все высшего порядка ÷A Счетчик бит выше «а» равен 0.

3. Допустим, что ÷N счетчик и ÷A Счетчик (с игнорированием всех битов более высокого порядка выше «а»), объединенный в один двоичный счетчик длиной n+a бит (n = количество ступеней делителя в Счетчик ÷N). Старший бит этого «гипотетического» счетчика должен соответствовать старшему разряду ÷N, а LSB должен соответствовать LSB ÷A. Системное делительное значение NT теперь получается, когда значение NT в двоичном формате используется для программирования «нового» n+a битового счетчика.

Используя два устройства, можно получить несколько значений двойного модуля.

5. Размеры