Макет для экспериментов с синтезатором частоты AD9852 фирмы Analog Devices

Charlos Potma, Cape Canaveral,USA

Новый генератор с прямым цифровым синтезом частоты (DDS) фирмы Analog Devices вызывает большой интерес у радиолюбителей. AD9852 и его брат - AD9854 могут синхронизироваться частотой до 300 MHz, что совместно с хорошим выходным фильтром позволяет строит генераторы с частотой вплоть до 120 MHz.

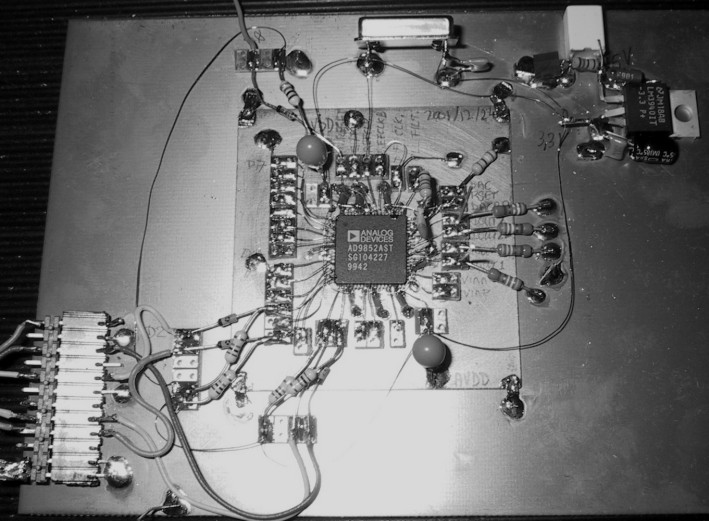

Я сделал макетную плату на DDS AD9852AST, с вариантом, который синхронизировался частотой 200 MHz. Можно применить 300 MHz версию синтезатора - AD9852ASQ, который имеет термоплощадку на корпусе для отвода тепла.

Для управления синтезатором AD9852 через параллельный (LPT) порт компьютера написана небольшая программа (ad9852.zip) на Delphi. Эта программа учитывает вход частоты синхронизации, вычисляет выходную частоту DDS и осуществляет последующее программирование AD9852. Также возможно активизировать встроенный PLL синхро-умножитель, чтобы достигнуть более высокой частоты синхронизации при низкой частоте синхронизации.

| Небольшое предупреждение: наблюдайте за температурой чипа! Программа позволяет выставить частоту синхронизации 300 MHz, но Вы должны постоянно контролировать ее температуру, чтобы не перегреть микросхему. Перегрев приводит к мгновенному ее уничтожению! |

Программа управления выводит на дисплей расчет 48-битное слово настройки частоты в различных форматах.

Исходный код программы содержит идею вычисления кода настройки. За исключением слова настройки частоты, все байты посланные на AD9852 показываются в списке.

Программа также учитывает выходной уровень ЦАП, используя 12-битное (0-4095) слово. Следующий выходной уровень ЦАП может также определяться в 12-битовом 2's-дополнительном формате. Выход ЦАП - это постоянное напряжение. Это может быть использовано для генерации X-напряжения, когда AD9852 используется в "sweeper" приложении.

Программа инициализации AD9852 после общего сброса активизирует только цифровую секцию и ЦАП. Фильтр синхронизации не активизирован. Микросхема AD9852 может перезапускаться в любое время кнопкой "DDS Master Reset". После каждого изменения одного из входных полей необходимо нажать кнопку "Send data to DDS" (послать данные на DDS), чтобы передать управляющее слово на AD9852 с установленной и вычисленной частотой.

После основного сброса, чип устанавливается по умолчанию во внутренний режим коррекции, означая, что входные данные посланы из входных буферных регистров до цифровой электрической схемы. Это можно проверить контролируя импульсы коррекции на выоде 20 (I/O UD), который сконфигурирован как выход после основного сброса. Хотя внутренний перезапуск может быть и полезным, я решил инициализировать чип, используя внешний способ перезапуска, чтобы фактический момент коррекции определялся управляющей программой. После перезапуска чипа внешним способом, импульсы на штырьке 20 пропадают и этот вывод устанавливается в режим ввода данных. Микросхема AD9852 может повредиться, если этот штырек непосредственно подключается к любому внешнему источнику, который заземлен. Дело в том, что 3-вольтовые выходные импульсы в этом случае шунтируются и выходной ток этого вывода может быть превышен. Резистор номиналом 1 кОм устанавливает этот ток на безопасный максимум 3 mA.

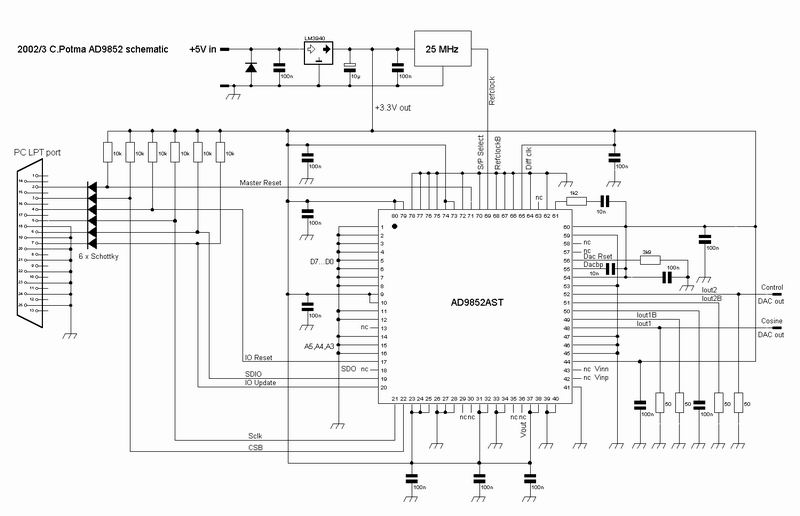

На приведенной схеме представлен интерфейс между 5-ти вольтовым параллельным портом компьютера и 3,3 вольтовой микросхемой AD9852. Этот интерфейс позаимствован из схемы аналогичного проекта от OH8RO.

(Для увеличения схемы "кликните" на ней.)

Резисторы 10 кОм установлены на линиях 3.3 V, тогда как диоды Шотки изолируют 5 вольтовый уровень параллельного порта от 3,3 вольтового уровня синтезатора AD9852. Диоды Шотки также устанавливают 'нулевой уровень' входных линий в 0.3 Вольта.

Я использовал интегральный стабилизатор LM3940 как 3.3 регулятор напряжения. Схема показывает только один регулятор, но в практическом применении желательно три: один для модуля синхронизации, второй для AD9852 и третий для цифровой мощного блокя. Эти регуляторы должны быть хорошо изолированы друг друга, чтобы улучшить SFDR.

Микросхема AD9852 программируется используя последовательный режим ввода данных. Это установливается заземлением вывода 70 (S/P SELECT). При этом штырьки 1-8 (D7-D0: двунаправленные входы данных параллельного программирования) не использованы и заземлены. Штырьки 17, 19 и 20 (IO RESET, SDIO и I/O UD) используются, чтобы синхронизировать биты данных в чипе. Эти выводы также функционируют с портом А (Parallel Address Inputs). Вывод 18 (SDO) не использован и висит в воздухе. Выводы 14, 15 и 16 (A5, A4 и A3) не использованы и заземлены. Вывод 21 (SCLK) задействован для частоты синхронизации. Вывод 22 (CSB) - как выбор микросхемы.

Я использовал 25 MHz модуль синхронизации. Конечно можно использовать и другие задающие генераторы частоты. Частота синхронизации является параметром в управляющей программе, так что она может быть изменена по желанию. Чип устанавливается для несимметричного входа синхронизации, заземлением выводов 64 (DIFF CLK) и 68 (REFCLKB) и непосредственной подачи сигналас выхода модуля синхронизации на вывод 69 (REFCLK). Большинство модульных генераторов разработанно для питания напряжением 5 Вольт, но могут работать и при 3.3 В.

Микросхема AD9852 смонтирована на небольшой плате из фольгированного стеклотекстолита, где слой меди использован как заземляющая площадка. Все выводы не подключенные к земле немного подогнуты вверх. Все заземленные выводы паяются непосредственно на заземляющей площадке. Все силовые выводы блокируются 100nF SMD-конденсаторами непосредственно с вывода микросхемы на землю. Остальные выводы соеденены тонким эмалированным проводом с вырезанными площадками фольги, это позволяет легко модифицировать конфигурацию чипа. Выход ЦАП иметь нефильтрованны 50 Омный выход. Схема в основном соответствует описанию AD9852, представленному фирмой на сайте фирмы Analog Devices.

Оригинал статьи на английском языке.

Перевод Николая Большакова (RA3TOX), ноябрь 2002 г.